# Transient Thermal and Electrical Co-Optimization of BEOL Top-Gated ALD In<sub>2</sub>O<sub>3</sub> FETs Toward Monolithic 3-D Integration

Pai-Ying Liao<sup>®</sup>, Dongqi Zheng, Sami Alajlouni<sup>®</sup>, Zhuocheng Zhang<sup>®</sup>, Mengwei Si<sup>®</sup>, *Member, IEEE*, Jie Zhang<sup>®</sup>, *Member, IEEE*, Jian-Yu Lin, Tatyana I. Feygelson, Marko J. Tadjer<sup>®</sup>, *Senior Member, IEEE*, Ali Shakouri, and Peide D. Ye<sup>®</sup>, *Fellow, IEEE*

Abstract-In this work, the transient thermal and electrical characteristics of top-gated (TG), ultrathin, atomic-layer-deposited (ALD), back-end-of-line (BEOL) compatible indium oxide (In2O3) transistors on various thermally conductive substrates are co-optimized by visualization of the self-heating effect (SHE) utilizing an ultrafast high-resolution (HR) thermo-reflectance (TR) imaging system and overcome the thermal challenges through substrate thermal management and short-pulse measurement. At the steady-state, the temperature increase ( $\triangle T$ ) of the devices on highly resistive silicon (HR Si) and diamond substrates are roughly 6 and 13 times lower than that on a SiO<sub>2</sub>/Si substrate, due to the much higher thermal conductivities ( $\kappa$ ) of HR Si and diamond. Consequently, the ultrahigh drain current ( $I_D$ ) of 3.7 mA/ $\mu$ m at drain voltage  $(V_{DS})$  of 1.4 V with direct current (dc) measurement is achieved with TG ALD In<sub>2</sub>O<sub>3</sub> FETs on a diamond substrate. Furthermore, transient thermal study shows that it takes roughly 350 and 300 ns for the devices to heat-up and cool-down to the steady-states, being independent of the substrate. The extracted thermal time constants of heatup  $(\tau_h)$  and cool-down  $(\tau_c)$  processes are 137 and 109 ns, respectively. By employing electrical short-pulse measurement with a pulsewidth ( $t_{pulse}$ ) shorter than  $\tau_h$ , the SHE

Manuscript received 16 November 2022; revised 31 December 2022; accepted 4 January 2023. Date of publication 16 January 2023; date of current version 24 March 2023. This work was supported in part by the Semiconductor Research Corporation (SRC), Nanoelectronic Computing Research (nCORE) Innovative Materials and Processes for Accelerated Compute Technologies (IMPACT) Center and in part by the Applications and Systems driven Center for Energy-Efficient Integrated NanoTechnologies (ASCENT) Center through the SRC/Defense Advanced Research Projects Agency (DARPA) Joint University Microelectronics Program (JUMP). This article is an extended version of a paper presented at IEDM 2022. The review of this article was arranged by Editor D. Triyoso. (Corresponding author: Peide D. Ye.)

Pai-Ying Liao, Dongqi Zheng, Sami Alajlouni, Zhuocheng Zhang, Mengwei Si, Jie Zhang, Jian-Yu Lin, Ali Shakouri, and Peide D. Ye are with the School of Electrical and Computer Engineering and the Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907 USA (e-mail: yep@purdue.edu).

Tatyana I. Feygelson and Marko J. Tadjer are with the Electronics Science and Technology Division, United States Naval Research Laboratory, Washington, DC 20375 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TED.2023.3235313.

Digital Object Identifier 10.1109/TED.2023.3235313

can be significantly reduced. Accordingly, a higher  $I_D$  of 4.3 mA/ $\mu$ m is realized with a 1.9-nm-thick  $\ln_2 O_3$  FET on HR Si substrate after co-optimization. Besides, to integrate BEOL-compatible ALD  $\ln_2 O_3$  transistors on the front-end-of-line (FEOL) devices with the maintenance of the satisfactory heat dissipation capability, a FEOL-interlayer-BEOL structure is proposed where the interlayer not only electrically isolates the FEOL and BEOL devices but also serves as a thermally conductive layer to alleviate the SHE.

Index Terms—Atomic layer deposition, indium oxide (In<sub>2</sub>O<sub>3</sub>), self-heating effect (SHE), thermal engineering, thermo-reflectance (TR).

# I. INTRODUCTION

ESPITE the wide application in the display industry [1], oxide semiconductors attract more interest recently as back-end-of-line (BEOL)-compatible channel materials for thin-film transistor (TFT) applications even toward monolithic 3-D (M3D) integration [2], [3], [4], [5], [6], [7], [8], [9], [10], [11], [12], [13], [14], [15], [16], [17]. Among them, atomic-layer-deposited (ALD) indium oxide (In<sub>2</sub>O<sub>3</sub>) is of great interest due to its outstanding properties such as wafer-scale uniformity, high carrier mobility, BEOL compatibility, ambient stability, and capability of conducting ultrahigh current. Especially, the ALD growth method provides not only the angstrom-scale thickness control but also the atomically smooth surface conformality on 3-D surface structures such as deep trenches and side walls [2], [3], [4], [5], [6], [7], [8]. It has been demonstrated that back-gated (BG) ALD In<sub>2</sub>O<sub>3</sub> transistors can be realized with an ultra-thin body of 0.5 nm, which is only a couple of atoms thick [6]. Besides, a high drain current ( $I_D$ ) up to 2.2 mA/ $\mu$ m at drain bias  $(V_{DS})$  of 0.7 V is reached by 1.5-nm-thick BG  $In_2O_3$ devices operated at enhancement mode (E-mode) [14].

Nevertheless, even though top-gated (TG) devices are particularly desired for practical applications, the explorations of  $In_2O_3$  FETs mostly focus on BG structure. This is mainly due to the two challenges of defect induction during the formation of the high-k TG dielectric and severe self-heating

0018-9383 © 2023 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

effect (SHE) with high power density (PD) [7], [8]. The root cause of the former issue is that the formation of the high-k dielectric stack, ALD HfO<sub>2</sub>, likely fetches oxygen not only from the oxygen precursor but also the In<sub>2</sub>O<sub>3</sub> channel underneath, which induces oxygen vacancies at the channel. Fortunately, this can be partly resolved by lowering the growth temperature of ALD HfO<sub>2</sub> from 200 °C down to 120 °C, followed by rapid thermal annealing (RTA) treatment in the O<sub>2</sub> environment [5], [8]. On the other hand, the latter challenge remains a bottleneck of TG ALD In<sub>2</sub>O<sub>3</sub> devices.

In this work, an ultrafast high-resolution (HR) thermoreflectance (TR) imaging system is introduced to visualize the transient and steady-state characteristic  $\Delta T$  of TG In<sub>2</sub>O<sub>3</sub> devices on different substrates to address the thermal issues. The substrate substitution method [7] is first applied to alleviate SHE. At the steady states, the SHE is mitigated by a factor of 6 and 13 with HR Si and diamond substrate, respectively, compared to SiO<sub>2</sub>/Si substrate. Next, in order to understand the transient thermodynamics of the selfheating process of TG ALD In<sub>2</sub>O<sub>3</sub> transistors, transient TR measurement is performed. The extracted time constants  $\tau_h$ and  $\tau_c$  are roughly 137 and 109 ns, respectively. By resolving SHE, an ultrahigh  $I_D$  of 3.7 mA/ $\mu$ m is realized with 2.5-nm-thick In<sub>2</sub>O<sub>3</sub> devices on the diamond substrate under direct current (dc) measurement. Furthermore, by pulse measurement with pulse widths shorter than  $\tau_h$ , even higher  $I_D$ of 4.3 mA/ $\mu$ m is achieved with 1.9-nm-thick In<sub>2</sub>O<sub>3</sub> transistors on HR Si substrate under pulse measurement. Besides, BEOLcompatible TG ALD In<sub>2</sub>O<sub>3</sub> transistors are built on top of front-end-of-line (FEOL) Si devices with a thick plasmaenhanced chemical-vapor-deposited (PECVD) silicon nitride  $(SiN_x)$  in between, showing potentials of combining FEOL devices with BEOL devices together toward M3D integration. This article is an extended version of an accepted 2022 IEEE International Electron Devices Meeting (IEDM 2022) paper with more details and FEOL-BEOL integration included.

# II. DEVICE FABRICATION AND PERFORMANCE

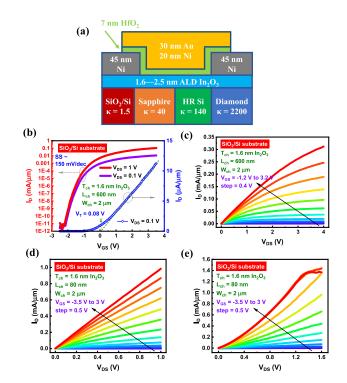

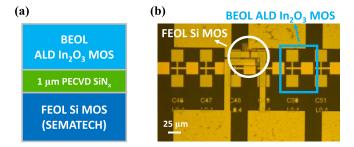

Fig. 1(a) exhibits the schematic of TG ALD In<sub>2</sub>O<sub>3</sub> transistors. Different  $\kappa$ -value substrates including SiO<sub>2</sub>/Si, sapphire, HR Si, and diamond from 1.5 to 2200 W·m<sup>-1</sup>·K<sup>-1</sup>, are used. After solvent cleaning, a 1.6–2.5 nm In<sub>2</sub>O<sub>3</sub> layer was conformally grown by ALD at 225 °C with trimethylindium (TMIn) and H<sub>2</sub>O as the In and O precursors, respectively, followed by an Ar/BCl<sub>3</sub> dry-etching step for device isolation. Then, 45 nm Ni was deposited as source/drain (S/D) contacts by e-beam lithography (EBL), e-beam evaporation, and a lift-off step. Next, a 7 nm HfO<sub>2</sub> top dielectric layer was formed by ALD at 120 °C with [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf (TDMAHf) and H<sub>2</sub>O as the Hf and O precursors, respectively. Finally, the top-gate metal of 30/20 nm Au/Ni was deposited with the same process as the S/D metal, followed by an RTA treatment at 250 °C-300 °C in an O<sub>2</sub> environment for 2-4 min. The overall thermal budget is as low as 300 °C, making it BEOL-compatible.

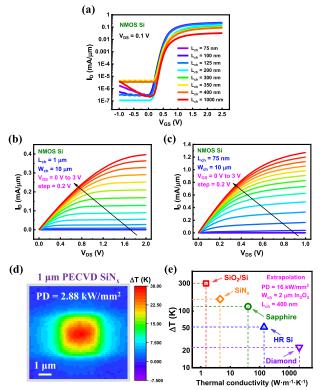

Fig. 1(b) and (c) presents the electrical characteristics of a TG ALD  $In_2O_3$  FET with a channel length ( $L_{ch}$ ) of 600 nm and a thin channel thickness ( $T_{ch}$ ) of 1.6 nm on a SiO<sub>2</sub>/Si sub-

Fig. 1. (a) Device schematic of a TG ALD  $\ln_2 O_3$  FET with various thermally conductive substrates. The unit of thermal conductivity  $(\kappa)$  is W·m<sup>-1</sup>·K<sup>-1</sup>. (b) Transfer. (c) Output characteristics of a TG ALD  $\ln_2 O_3$  FET with  $\log L_{\rm ch}$  of 600 nm and thin  $T_{\rm ch}$  of 1.6 nm on a SiO<sub>2</sub>/Si substrate operated at enhancement-mode (E-mode). ON-OFF ratio of 10 orders of magnitude and SS value of 150 mV/dec are performed. (d) Output characteristics of a TG ALD  $\ln_2 O_3$  FET with short  $L_{\rm ch}$  of 80 nm on a SiO<sub>2</sub>/Si substrate. (e) Severe SHE deteriorates the device performance of a TG ALD  $\ln_2 O_3$  FET with high PD.

strate operated at enhancement-mode. The extracted threshold voltage  $(V_T)$  and subthreshold swing (SS) are 0.08 V and 150 mV/dec, respectively. ON/OFF ratio of 10 orders of magnitude is obtained due to the wide bandgap of In<sub>2</sub>O<sub>3</sub>, indicating great switching behaviors. Fig. 1(d) shows the  $I_D$ – $V_{DS}$  curves of a similar device with a shorter  $L_{ch}$  of 80 nm, exhibiting a maximum  $I_D$  of 1 mA/ $\mu$ m at  $V_{DS}$  of 1 V which is much higher than the long channel devices. However, as the applied  $V_{\rm DS}$  increases to 1.6 V as shown in Fig. 1(e), serious SHE happens due to low- $\kappa$  of SiO<sub>2</sub>, and the device becomes unstable. The curves perform Schottky-like behaviors, and the current gradually deteriorates with higher and higher PD. This is the thermal bottleneck for high  $I_D$  In<sub>2</sub>O<sub>3</sub> FETs, and therefore, the ultrafast HR TR imaging system is introduced in the following sections to visualize and resolve the thermal challenges.

## III. STEADY-STATE CHARACTERIZATION

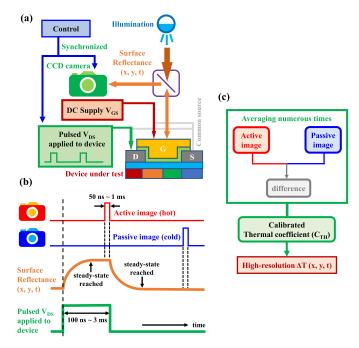

The ultrafast HR TR imaging equipment employed to systematically investigate and resolve the SHE is illustrated in Fig. 2(a). During the measurement, the device under test is applied by periodic  $V_{\rm DS}$  pulses and a constant  $V_{\rm GS}$  bias, where the source is common, to induce the SHE. A high-speed green light LED (wavelength of 530 nm) is equipped to illuminate the device surface for the synchronized charge-coupled device (CCD) camera to capture the surface reflectance. Fig. 2(b) demonstrates its working mechanism. As  $V_{\rm DS}$  pulses start,

Fig. 2. (a) Schematic illustration of the ultrafast HR TR imaging system setup. (b) Working mechanism of the ultrafast HR TR imaging equipment in time domain. (c) Transformation from TR signal to a temperature scale.

the device is turned on and accordingly self-heats up, and TR signals are captured as an active image after the steady-state is reached as shown in red. Similarly, when  $V_{\rm DS}$  pulses end, the device is turned off and hence naturally cools down to ambient temperature, and TR signals are captured as a passive image after the steady-state is reached as shown in blue. This process is repeated numerous times, and the difference between the active and passive images is averaged consequently and transformed into a temperature scale by dividing by the calibrated thermal coefficient of the surface material ( $C_{\rm TH} = -2.5 \times 10^{-4} \ {\rm K}^{-1}$  [18], [19], [20]) to obtain the final HR  $\Delta T$  distribution image at the steady-state as shown in Fig. 2(c).

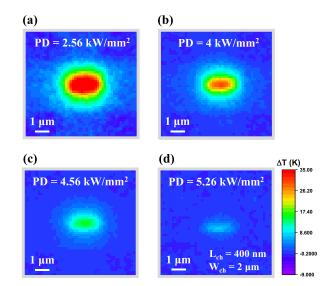

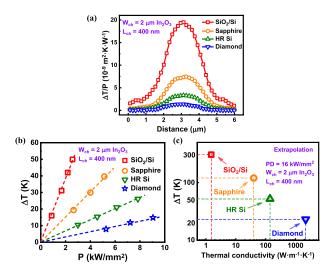

Fig. 3 presents the observed  $\Delta T$  distribution of the TG In<sub>2</sub>O<sub>3</sub> transistors around the channel region. All the devices under test have identical structures and dimensions of 400 nm  $L_{\rm ch}$  and 2  $\mu$ m  $W_{\rm ch}$ , and the only difference is the substrate in use. Clearly, the one on a SiO<sub>2</sub>/Si substrate is the most self-heated while the one on a diamond substrate is the least. The cross sections of the  $\Delta T$  along the channel width  $(W_{ch})$ direction normalized by PD is demonstrated in Fig. 4(a) where the PD is calculated by  $(I_D \times V_{DS})/(L_{ch} \times W_{ch})$ . Similar bell-like shapes are observed in all the cases. The maximum  $\Delta T$  of the devices with individual substrates and different PD is plotted in Fig. 4(b) where a linear relationship is obtained despite the substrate. The inversed slopes of the regression lines indicate the capability of the substrate to dissipate the generated Joule heat in the channel. To compare the thermal dissipation capabilities of the substrates, the  $\Delta T$  is extrapolated to a constant PD of 16 kW/mm<sup>2</sup> in each case as shown in Fig. 4(c). Fig. 4(c) implies that the higher  $\kappa$  of the substrate is, the lower the maximum normalized  $\Delta T$  will be. Sapphire  $(\kappa = 40 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1} \text{ [21]}), \text{ HR Si } (\kappa = 140 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1} \text{ [22]}),$

Fig. 3. SHE visualization of TG  $In_2O_3$  FETs in experiments with substrates of (a)  $SiO_2/Si$ , (b) sapphire, (c) highly resistive Si, and (d) diamond with various PD. The  $L_{\rm ch}$  and  $W_{\rm ch}$  are 400 nm and 2  $\mu$ m, respectively, for all the devices. The device on a  $SiO_2/Si$  substrate is the most self-heated while the one on a diamond substrate is the least.

Fig. 4. (a) Cross sections of PD-normalized  $\Delta T$  of TG ALD  $\ln_2 O_3$  FETs with different substrates. (b)  $\Delta T$  extraction of TG ALD  $\ln_2 O_3$  devices with different substrates and power densities. Linear relationship is agreed in all the cases. (c) Comparison of the extrapolated  $\Delta T$  with different substrates given a constant PD.

and diamond ( $\kappa = 2200 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$  [23]) substrates have  $\Delta T$  reduction by factors of 2.5, 6, and 13, respectively, compared with SiO<sub>2</sub>/Si substrate with thick SiO<sub>2</sub> ( $\kappa = 1.5 \text{ W} \cdot \text{m}^{-1} \cdot \text{K}^{-1}$  [24]).

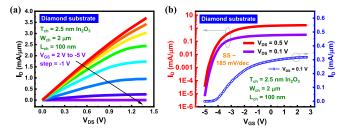

Motivated by the thermal studies, an  $In_2O_3$  transistor with  $T_{\rm ch}$  of 2.5 nm and  $L_{\rm ch}$  of 100 nm is built up on a diamond substrate to alleviate SHE. Fig. 5 presents its dc output and transfer characteristics where an ultrahigh  $I_D$  of 3.7 mA/ $\mu$ m is realized at  $V_{\rm DS}$  of 1.4 V without observable SHE even with high PD, in great contrast to Fig. 1(e). The extracted field-effect mobility ( $\mu_{\rm FE}$ ) and SS are 55.6 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> and 185 mV/dec, respectively. Note that the degradation of the transfer characteristics from Figs. 1(b) to 5(b) is due to the much thicker  $T_{\rm ch}$  as the electrical properties such as  $V_T$ ,

Fig. 5. (a) Output and (b) transfer characteristics of an  $In_2O_3$  FET with  $L_{ch}$  of 100 nm and  $T_{ch}$  of 2.5 nm on a diamond substrate, performing ultrahigh  $I_D$  of 3.7 mA/ $\mu$ m under dc condition.

ON-OFF ratio, and SS value of ALD  $In_2O_3$  devices are sensitively  $T_{ch}$ -dependent [2], [3], [4], [5], [6], [7].

# IV. TRANSIENT CHARACTERIZATION

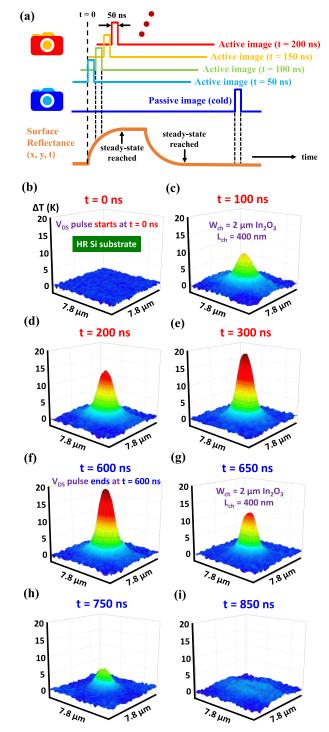

Although diamond with ultrahigh  $\kappa$  is an excellent heat sinker, it is not economically affordable for mass production. TG transistors on Si substrate are much more practically desired. To further mitigate the SHE on a Si substrate, detailed transient thermal characteristics are studied. Fig. 6(a) illustrates the working mechanism for transient thermal characteristics. Similar to steady-state measurements, an active and a passive image are captured by the synchronized CCD camera in each period. The difference is that steady-state investigations only take active images after the steady-state is reached, while transient-state explorations take them throughout the whole process. By setting the active image to be captured at a specific time, the  $\Delta T$  distribution of that moment can be obtained through the same process shown in Fig. 2(c).

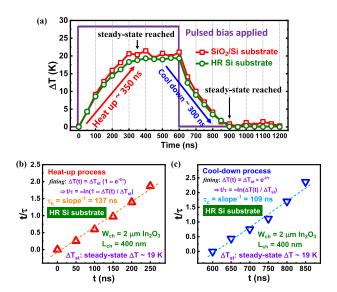

To experimentally observe the time-resolved self-heat-up and cool-down processes, the  $V_{\rm DS}$  pulses are set to start at 0 ns and end at 600 ns. Besides, the image capture time window is decreased to 50 ns, which is the minimum of the equipment capability and will be the resolution of the time-resolved measurement. From t = 0–1200 ns, TR images are taken every 50 ns. The heat-up process is illustrated in Fig. 6(b)-6(e) where the  $V_{DS}$  pulses begin at t=0 ns. The  $\Delta T$  distribution around the channel region gradually increases after then due to SHE, and the transient process is observed. Similarly, the  $V_{DS}$  pulses end at t = 600 ns, and the  $\Delta T$ peak introduced by SHE gradually decreases as shown in Fig. 6(f)-6(i). The maximum  $\Delta T$  of each moment of the devices with SiO<sub>2</sub>/Si and HR Si substrates are summarized in Fig. 7(a). Two devices with the same structure and dimensions of 400 nm  $L_{\rm ch}$  and 2  $\mu$ m  $W_{\rm ch}$  but different substrates are measured. It takes roughly 350 and 300 ns to reach steadystates for heat-up and cool-down, no matter whether SiO<sub>2</sub>/Si or HR Si serves as the substrate.

By assuming the processes satisfy Newton's law of cooling [25] (the rate of heat transfer is proportional to the temperature difference between the body and its surroundings) and utilizing their individual initial conditions, the following equations can be derived [26]:

$$\Delta T(t) = \Delta T_{\rm st} \times (1 - e^{-t/\tau})$$

for heating-up and

$$\Delta T(t) = \Delta T_{\rm st} \times e^{-t/\tau}$$

Fig. 6. (a) Working mechanism of transient thermal property study with an ultrafast HR TR imaging system. (b)–(i) Transient TR characteristics of a TG ALD  $\rm In_2O_3$  FET on HR Si substrate. The device was self-heated-up by applying a  $V_{\rm DS}$  pulse starting at 0 ns and ending at 600 ns. (b)–(e) Demonstrate the heat-up process while (f)–(i) demonstrate the cool-down process.

for cooling down where  $\Delta T(t)$  represents the  $\Delta T$  at time t,  $\Delta T_{\rm st}$  represents the steady-state  $\Delta T$ , and  $\tau$  represents the thermal time constant. Accordingly, the following equations are obtained:

$$\frac{t}{\tau_h} = -\ln\left(1 - \frac{\Delta T(t)}{\Delta T_{\rm st}}\right)$$

Fig. 7. (a) Transient  $\Delta T$  results and comparison with different substrates. Roughly 325 ns is needed to reach steady-state in both cases. Time constant extraction of (b) heat-up and (c) cool-down processes from the transient  $\Delta T$  measurement results with HR Si substrate of Fig. 7(a). The  $t/\tau$  values are obtained by plugging the measured individual  $\Delta T(t)$  values into the indicated formulas.

for heating-up and

$$\frac{t}{\tau_c} = -\ln\!\left(\frac{\Delta T(t)}{\Delta T_{\rm st}}\right)$$

for cooling-down where  $\tau_h$  and  $\tau_c$  represent the heatup and cool-down thermal time constant, respectively. Fig. 7(b) and (c) demonstrates the calculated  $t/\tau$  values by plugging the experimentally observed data points in Fig. 7(a) at time t into the dedicated equations. The heat-up and cool-down thermal time constants,  $\tau_h$  and  $\tau_c$ , can be consequently acquired by extracting the inversed slopes of the regression lines in Fig. 7(b) and (c), respectively. Finally,  $\tau_h$ and  $\tau_c$  are extracted to be 137 and 109 ns, respectively.

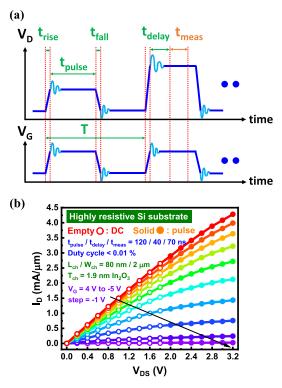

With the understanding of its transient thermal characteristics, short-pulse electrical co-optimization is proposed to alleviate SHE. Fig. 8(a) exhibits the working principles of pulse measurement in the time domain where both the drain and gate biases are pulses instead of constant. At the start of each pulse,  $t_{rise}$  of time is used for setting the biases to the desired values. Then, they last for  $t_{\text{pulse}}$  of time in which the first  $t_{\text{delay}}$  of time is used for bias stabilization, and the following  $t_{\text{meas}}$  of time is used for current measurement. The  $t_{\rm delay}$  time is required as the biases show some damping after being changed. After  $t_{\text{pulse}}$ ,  $t_{\text{fall}}$  of time is used for setting the biases back to zero, and they stay zero until the start of the next cycle. By applying pulse measurement, the device under test is only turned on for  $t_{\text{pulse}}$  of time each cycle. As long as  $t_{\text{pulse}}$  is short enough, the device under test is turned off before SHE degrades the device's performance. Hence, the SHE can be mostly avoided.

Fig. 8(b) exhibits the  $I_D$ – $V_{DS}$  curves of a TG In<sub>2</sub>O<sub>3</sub> FET with  $T_{\rm ch}$  of 1.9 nm and  $L_{\rm ch}$  of 80 nm on the HR Si substrate. The empty symbols represent the dc measurement results where  $V_{\rm DS}$  up to 1.8 V can be applied to achieve  $I_D$  up to

Fig. 8. (a) Diagram sketch of pulse measurement setup in time domain. The light blue damping illustrates the bias stabilization process after being set to desired values. (b) Output characteristics of a TG ALD  $\ln_2 O_3$  FET with short  $L_{\rm ch}$  of 80 nm and  $T_{\rm ch}$  of 1.9 nm on HR Si substrate achieving extremely high  $I_D$  up to 4.3 mA/ $\mu m$  with short-pulse measurement.

Fig. 9. (a) Structure illustration of combining BEOL ALD  $In_2O_3$  transistors and FEOL Si devices with 1- $\mu$ m-thick PECVD  $SiN_x$ . (b) Optical photograph of the structure in (a) where the indicated FEOL and BEOL devices are vertically separated by a 1- $\mu$ m-thick PECVD  $SiN_x$  layer.

2.6 mA/ $\mu$ m without observable SHE in its electrical performance. Nonetheless, SHE starts to take place with larger  $V_{\rm DS}$  with dc biases. On the other hand, the solid symbols represent the pulse-measurement results with  $t_{\rm pulse}$  of 120 ns. With short-pulse measurement, an ultrahigh  $I_D$  of 4.3 mA/ $\mu$ m is achieved at a higher  $V_{\rm DS}$  of 3.2 V. In great contrast to Fig. 1(d), even with such high PD on an atomically thin channel, there is no observable SHE since the  $t_{\rm pulse}$  of 120 ns is even shorter than a heat-up thermal time constant,  $\tau_h$ , of 137 ns. The key fact is that the electrical response is much faster than the thermal response. Short-pulse electrical measurement can significantly reduce SHE and probe the potential of the material and device performance.

Besides,  $SiN_x$  is able to serve as a promising interlayer dielectric for M3D integration due to its relatively high

Fig. 10. (a) Transfer characteristics of the FEOL Si nMOS, showing decent switching behaviors and E-mode operation. (b) Corresponding output characteristics of a long channel device with  $L_{\rm ch}$  of 1  $\mu$ m, performing great saturation behaviors. (c) Similar  $I_D$ – $V_{\rm DS}$  curves of a short channel device with  $L_{\rm ch}$  of 75 nm, exhibiting high  $I_D$  of 1.2 mA/ $\mu$ m at  $V_{\rm DS}$  of 1 V. (d)  $\Delta$  T distribution of a TG In<sub>2</sub>O<sub>3</sub> transistor with channel thickness of 1.8 nm shown in Fig. 9(b). (e) Comparison of the extrapolated  $\Delta$  T with different substrates including PECVD SiN $_X$  given a constant PD.

thermal conductivity (4.5 W·m<sup>-1</sup>·K<sup>-1</sup> [27]), low leakage current [28], [29], great CMOS compatibility [30], and low growth temperature enabled by PECVD [31], [32]. To integrate BEOL-compatible TG ALD  $In_2O_3$  TFTs on the FEOL devices, a 1- $\mu$ m-thick layer of SiN $_x$  was grown by PECVD at a low temperature of 150 °C as an interlayer on SEMATECH chips with Si transistors to maintain decent heat dissipation capability. TG ALD  $In_2O_3$  transistors were then fabricated on top of the thick SiN $_x$  interlayer as illustrated in the diagram sketch of Fig. 9(a). Fig. 9(b) exhibits an optical image of the fabricated devices where a FEOL Si device and a BEOL ALD  $In_2O_3$  device are indicated in the white circle and blue square, respectively. The FEOL and BEOL transistors are separated by a 1- $\mu$ m-thick SiN $_x$  layer in between for satisfactory electrical insulation.

Fig. 10(a) shows the transfer characteristics of the SEMAT-ECH E-mode Si nMOS with variant  $L_{\rm ch}$  from 75 nm to 1  $\mu$ m at  $V_{\rm DS}$  of 0.1 V where great switching behaviors are exhibited regardless of  $L_{\rm ch}$ . ON-OFF ratios range from 4 to 6 orders of magnitude, and SS values are all approximately 90–110 mV/dec. Fig. 10(b) illustrates the corresponding output characteristics of a long channel device with  $L_{\rm ch}$  of 1  $\mu$ m where exceptional saturation properties are exhibited. Besides, Fig. 10(c) similarly reveals the  $I_D$ - $V_{\rm DS}$  curves of a device with a short  $L_{\rm ch}$  of 75 nm which reaches a high  $I_D$  of 1.2 mA/ $\mu$ m at  $V_{\rm DS}$  of 1 V. The electrical characterization of the FEOL Si devices was measured before the deposition of the SiN $_x$  layer

and the fabrication of the BEOL devices. Fig. 10(d) shows the TR measurement of a TG  $In_2O_3$  transistor with  $L_{ch}$  of 400 nm,  $W_{ch}$  of 2  $\mu$ m, and channel thickness of 1.8 nm in the FEOL-SiN<sub>x</sub>-BEOL structure. It is noticeable that the hottest region performs roughly wider  $\Delta T$  distribution compared with previous cases shown in Fig. 3, which might be due to the reflected heat from the  $SiN_x$ /FEOL interface to the surface with the presence of the 1- $\mu$ m-thick  $SiN_x$  layer. Fig. 10(e) illustrates the comparison of the thermal dissipation capability of the devices on PECVD  $SiN_x$  with that on other substrates, indicating that the PD-normalized  $\Delta T$  of  $In_2O_3$  transistors in the FEOL-SiN<sub>x</sub>-BEOL structure is approximately 1.9 times lower than that on a  $SiO_2$ /Si substrate.

Nevertheless, the TG ALD In<sub>2</sub>O<sub>3</sub> transistors fabricated on the SiN<sub>x</sub>-FEOL structure demonstrate poor switching behaviors with an ON-OFF ratio smaller than 1 order of magnitude. This is plausibly due to the defect-rich surface of the PECVD SiN<sub>x</sub> layer [33], [34], [35]. More investigations and efforts are needed to better realize the integration of FEOL and BEOL fabrications, but this work proposed the FEOL-interlayer-BEOL structure where the interlayer not only separates the FEOL and BEOL devices but also serves as a thermally conductive layer to alleviate the SHE of the BEOL ALD In<sub>2</sub>O<sub>3</sub> transistors. The realization of this structure also benefits the applications of ALD In<sub>2</sub>O<sub>3</sub> transistors toward M3D integrations at advanced technology nodes.

### V. CONCLUSION

In summary, transient thermal and electrical properties of TG ALD  $In_2O_3$  FETs on various thermally conductive substrates are co-optimized employing an ultrafast HR TR imaging technique to unveil the problematic SHE. By using HR Si substrate and electrical short-pulse measurement, an ultrahigh  $I_D$  of 4.3 mA/ $\mu$ m is achieved on atomically thin  $In_2O_3$  devices without observable SHE. This work demonstrates that the understanding of both thermal and electrical transient dynamics is important to resolve thermal bottleneck on atomically thin oxide semiconductor devices. Besides, a FEOL-interlayer-BEOL structure is proposed where the interlayer not only electrically isolates the FEOL and BEOL devices but also serves as a thermally conductive layer to alleviate the SHE and exhibit the potentials for the applications of BEOL ALD  $In_2O_3$  TFTs toward M3D integration.

## REFERENCES

- K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, "Amorphous oxide semiconductors for high-performance flexible thinfilm transistors," *Jpn. J. Appl. Phys.*, vol. 45, no. 5, pp. 4303–4308, Apr. 2006, doi: 10.1143/JJAP.45.4303.

- [2] M. Si et al., "Why In<sub>2</sub>O<sub>3</sub> can make 0.7 nm atomic layer thin transistors," *Nano Lett.*, vol. 21, no. 4, pp. 500–506, Jan. 2021, doi: 10.1021/acs.nanolett.0c03967.

- [3] M. Si, Z. Lin, A. Charnas, and P. D. Ye, "Scaled atomic-layer-deposited indium oxide nanometer transistors with maximum drain current exceeding 2 A/mm at drain voltage of 0.7 V," *IEEE Electron Device Lett.*, vol. 42, no. 2, pp. 184–187, Feb. 2021, doi: 10.1109/LED.2020.3043430.

- [4] M. Si, A. Charnas, Z. Lin, and P. D. Ye, "Enhancement-mode atomic-layer-deposited In<sub>2</sub>O<sub>3</sub> transistors with maximum drain current of 2.2 A/mm at drain voltage of 0.7 V by low-temperature annealing and stability in hydrogen environment," *IEEE Trans. Elec*tron Devices, vol. 68, no. 3, pp. 1075–1080, Mar. 2021, doi: 10.1109/TED.2021.3053229.

- [5] M. Si, Z. Lin, Z. Chen, and P. D. Ye, "High-performance atomic-layer-deposited indium oxide 3-D transistors and integrated circuits for monolithic 3-D integration," *IEEE Trans. Electron Devices*, vol. 68, no. 12, pp. 6605–6609, Dec. 2021, doi: 10.1109/TED.2021.3106282.

- [6] M. Si, Z. Lin, Z. Chen, X. Sun, H. Wang, and P. D. Ye, "Scaled indium oxide transistors fabricated using atomic layer deposition," *Nature Electron.*, vol. 5, no. 3, pp. 164–170, Feb. 2022, doi: 10.1038/s41928-022-00718-w.

- [7] P.-Y. Liao, M. Si, Z. Zhang, Z. Lin, and P. D. Ye, "Realization of maximum 2 A/mm drain current on top-gate atomic-layer-thin indium oxide transistors by thermal engineering," *IEEE Trans. Electron Devices*, vol. 69, no. 1, pp. 147–151, Jan. 2022, doi: 10.1109/TED.2021.3125923.

- [8] P.-Y. Liao et al., "Thermal studies of BEOL-compatible top-gated atomically thin ALD In<sub>2</sub>O<sub>3</sub> FETs," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2022, pp. 322–323.

- [9] J. Wu, F. Mo, T. Saraya, T. Hiramoto, and M. Kobayashi, "A monolithic 3D integration of RRAM array with oxide semiconductor FET for in-memory computing in quantized neural network AI applications," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.

- [10] W. Chakraborty, B. Grisafe, H. Ye, I. Lightcap, K. Ni, and S. Datta, "BEOL compatible dual-gate ultra thin-body W-doped indium-oxide transistor with  $I_{on}=370~\mu\text{A}/\mu\text{m}$ , SS = 73 mV/dec and  $I_{on}/I_{off}$  ratio  $>4\times10^9$ ," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.

- [11] S. Samanta, K. Han, C. Sun, C. Wang, A. V.-Y. Thean, and X. Gong, "Amorphous IGZO TFTs featuring extremely-scaled channel thickness and 38 nm channel length: Achieving record high  $G_{m,max}$  of 125  $\mu$ S/ $\mu$ m at  $V_{DS}$  of 1 V and  $I_{ON}$  of 350  $\mu$ A/ $\mu$ m," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2020, pp. 1–2.

- [12] S. Li et al., "Nanometre-thin indium tin oxide for advanced high-performance electronics," *Nature Mater.*, vol. 18, no. 10, pp. 1091–1097, Oct. 2019, doi: 10.1038/s41563-019-0455-8.

- [13] S. Subhechha et al., "Ultra-low leakage IGZO-TFTs with raised source/drain for V<sub>t</sub>>0 V and I<sub>on</sub> >30 μA/μm," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2022, pp. 292–293.

- [14] A. Charnas, M. Si, Z. Lin, and P. D. Ye, "Realization of enhancement-mode atomic-layer thin In<sub>2</sub>O<sub>3</sub> transistors with maximum current exceeding 2 A/mm at drain voltage of 0.7 V enabled by oxygen plasma treatment," *Appl. Phys. Lett.*, vol. 118, no. 5, Feb. 2021, Art. no. 052107, doi: 10.1063/5.0039783.

- [15] U. Chand et al., "Sub-10 nm ultra-thin ZnO channel FET with record-high 561 μA/μm I<sub>ON</sub> at V<sub>DS</sub> 1V, high μ-84 cm<sup>2</sup>/V-s and 1T-1RRAM memory cell demonstration memory implications for energy-efficient deep-learning computing," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2022, pp. 326–327.

- [16] J. Zhang et al., "Fluorine-passivated In<sub>2</sub>O<sub>3</sub> thin film transistors with improved electrical performance via low-temperature CF<sub>4</sub>/N<sub>2</sub>O plasma," *Appl. Phys. Lett.*, vol. 121, no. 17, Oct. 2022, Art. no. 172101, doi: 10.1063/5.0113015.

- [17] Z. Zhang et al., "A gate-all-around  $In_2O_3$  nanoribbon FET with near 20 mA/ $\mu$ m drain current," *IEEE Electron Device Lett.*, vol. 43, no. 11, pp. 1905–1908, Nov. 2022, doi: 10.1109/LED.2022.3210005.

- [18] K. Maize, A. Ziabari, W. D. French, P. Lindorfer, B. O'Connell, and A. Shakouri, "Thermoreflectance CCD imaging of self-heating in power MOSFET arrays," *IEEE Trans. Electron Devices*, vol. 61, no. 9, pp. 3047–3053, Sep. 2014, doi: 10.1109/TED.2014.2332466.

- [19] H. Zhou, K. Maize, J. Noh, A. Shakouri, and P. D. Ye, "Thermodynamic studies of β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane field-effect transistors on a sapphire substrate," ACS Omega, vol. 2, no. 11, pp. 7723–7729, Nov. 2017, doi: 10.1021/acsomega.7b01313.

- [20] J. Noh et al., "Enhancement of thermal transfer from β-Ga<sub>2</sub>O<sub>3</sub> nanomembrane field-effect transistors to high thermal conductivity substrate by inserting an interlayer," *IEEE Trans. Electron Devices*, vol. 69, no. 3, pp. 1186–1190, Jan. 2021, doi: 10.1109/TED.2022.3142651.

- [21] S. Burghartz and B. Schulz, "Thermophysical properties of sapphire, AlN and MgAl<sub>2</sub>O<sub>3</sub> down to 70 K," *J. Nucl. Mater.*, vol. 212, pp. 1065–1068, Sep. 1994, doi: 10.1016/0022-3115(94)90996-2.

- [22] H. R. Shanks, P. D. Maycock, P. H. Sidles, and G. C. Danielson, "Thermal conductivity of silicon from 300 to 1400 K," *Phys. Rev.*, vol. 130, pp. 1743–1748, Jun. 1963, doi: 10.1103/PhysRev. 130.1743.

- [23] J. R. Olson, R. O. Pohl, J. W. Vandersande, A. Zoltan, T. R. Anthony, and E. F. Banholzer, "Thermal conductivity of diamond between 170 and 1200 K and the isotope effect," *Phys. Rev. B, Condens. Matter*, vol. 47, no. 22, pp. 14850–14857, Jun. 1993, doi: 10.1103/PhysRevB.47.14850.

- [24] H.-C. Chien, D.-J. Yao, M.-J. Huang, and T.-Y. Chang, "Thermal conductivity measurement and interface thermal resistance estimation using SiO<sub>2</sub> thin film," *Rev. Sci. Instrum.*, vol. 79, no. 5, May 2008, Art. no. 054902, doi: 10.1063/1.2927253.

- [25] I. Newton, "Scala graduum caloris. Calorum descriptiones & figna," Philos. Trans. Roy. Soc., vol. 22, pp. 824–829, 1701.

- [26] R. W. Lewis, P. Nithiarasu, and K. N. Seetharamu, Fundamentals of the Finite Element Method for Heat and Fluid Flow. Hoboken, NJ, USA: Wiley, 2004.

- [27] P. Eriksson, J. Y. Andersson, and G. Stemme, "Thermal characterization of surface-micromachined silicon nitride membranes for thermal infrared detectors," *J. Microelectromech. Syst.*, vol. 6, no. 1, pp. 55–61, Mar. 1997, doi: 10.1109/84.557531.

- [28] M. Hua et al., "Characterization of leakage and reliability of SiN<sub>x</sub> gate dielectric by low-pressure chemical vapor deposition for GaN-based MIS-HEMTs," *IEEE Trans. Electron Devices*, vol. 62, no. 10, pp. 3215–3222, Sep. 2015, doi: 10.1109/TED.2015.2469716.

- [29] K. Sekine, Y. Saito, M. Hirayama, and T. Ohmi, "Highly robust ultrathin silicon nitride films grown at low-temperature by microwaveexcitation high-density plasma for giga scale integration," *IEEE Trans. Electron Devices*, vol. 47, no. 7, pp. 1370–1374, Jul. 2000, doi: 10.1109/16.848279.

- [30] A. Frigg et al., "Low loss CMOS-compatible silicon nitride photonics utilizing reactive sputtered thin films," Opt. Exp., vol. 27, pp. 37795–37805, Dec. 2019, doi: 10.1364/OE.380758.

- [31] H.-Y. Chang, C.-Y. Meng, C.-W. Huang, and S.-C. Lee, "The low-temperature a-SiN $_x$  films with high impermeability and high optical gap with application to organic light-emitting diode," *J. Appl. Phys.*, vol. 98, no. 8, Oct. 2005, Art. no. 084501, doi: 10.1063/1. 2089161

- [32] J. R. Lothian, F. Ren, S. J. Pearton, C. R. Abernathy, B. Tseng, and W. S. Hobson, "Low temperature SiN<sub>x</sub> as a sacrificial layer in novel device fabrication," *MRS Proc.*, vol. 300, pp. 161–167, Dec. 1993, doi: 10.1557/PROC-300-161.

- [33] S.-J. Tsai et al., "Approaching defect-free amorphous silicon nitride by plasma-assisted atomic beam deposition for high performance gate dielectric," Sci. Rep., vol. 6, pp. 1–9, Jun. 2016, doi: 10.1038/srep28326.

- [34] C. Zhang, M. Wu, P. Wang, M. Jian, J. Zhang, and L. Yang, "Stability of SiN<sub>x</sub> prepared by plasma-enhanced chemical vapor deposition at low temperature," *Nanomaterials*, vol. 11, no. 12, p. 3363, Dec. 2021, doi: 10.3390/nano11123363.

- [35] J. Kanicki and W. L. Warren, "Defects in amorphous hydrogenated silicon nitride films," J. Non. Cryst. Solids, vol. 164, pp. 1055–1060, Dec. 1993, doi: 10.1016/0022-3093(93)91180-B.